#### STATIC RANDOM-ACCESS MEMORIES

- Static Fully Decoded RAM's Organized as 256 Words of One Bit Each

- Schottky-Clamped for High Performance

- Choice of Three-State or Open-Collector Outputs

- Compatible with Most TTL and I<sup>2</sup>L Circuits

- Chip-Select Input Simplify External Decoding

- Typical Performance:

Read Access Time . . . 42 ns Power dissipation . . . 500 mW

## description

These 256-bit active-element memories are monolithic transistor-transistor logic (TTL) arrays organized as 256 words of one bit. They are fully decoded and have three chip-select inputs to simplify decoding required to achieve expanded system organizations.

#### write cycle

The information applied at the data input is written into the selected location when the chip-select inputs and the write-enable input are low. While the write-enable input is low, the 'S201 outputs are in the high-impedance state and the 'S301 outputs are off. When a number of outputs are bus-connected, this high-impedance or off state will neither load nor drive the bus line, but it will allow the bus line to be driven by another active output or a passive pull-up.

#### read cycle

The stored information (complement of information applied at the data input during the write cycle) is available at the output when the write-enable input is high and the three chip-select inputs is low. When any one of the chip-select inputs are high, the 'S201 outputs will be in the high-impedance state and the 'S301 outputs will be off.

### FUNCTION TABLE

| FUNCTION | INPUTS                          |   | 'S201                      | 'S301                      |  |  |

|----------|---------------------------------|---|----------------------------|----------------------------|--|--|

|          | CHIP SELECT WRITE ENABLE  S R/W |   | OUTPUT (Q)                 | OUTPUT (Q)                 |  |  |

| Write    | L                               | L | High Impedance             | Off                        |  |  |

| Read     | L                               | Н | Complement of Data Entered | Complement of Data Entered |  |  |

| Inhibit  | Н                               | X | High Impedance             | Off                        |  |  |

H = high level, L = low level, X = irrelevant

For chip-select:  $L \equiv all \ \overline{S}i$  inputs low,  $H \equiv all \ \overline{S}i$  inputs high

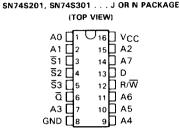

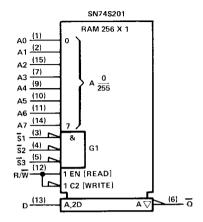

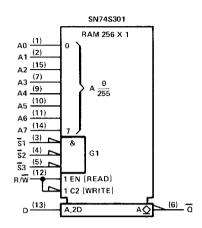

# logic symbols

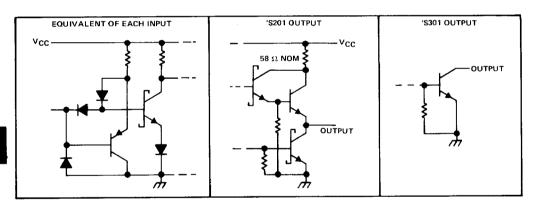

### schematics of inputs and outputs

၎

RAM

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)       | / |

|----------------------------------------|---|

| Input voltage                          | / |

| Off-State output voltage 5.5 \         | / |

| Operating free-air temperature range   | 2 |

| Storage temperature range65°C to 150°C | 2 |

# SN74S201, SN74S301 256-BIT HIGH-PERFORMANCE RANDOM-ACCESS MEMORIES

# recommended operating conditions

|                                                 |                                                                           | SN74S201 |     | SN74S301 |      |     | UNIT |      |  |

|-------------------------------------------------|---------------------------------------------------------------------------|----------|-----|----------|------|-----|------|------|--|

|                                                 |                                                                           | MIN      | NOM | MAX      | MIN  | NOM | MAX  | UNIT |  |

| Supply voltage, V <sub>CC</sub> (see Note 1)    |                                                                           | 4.75     | 5   | 5.25     | 4.75 | 5   | 5.25 | V    |  |

| High-level ou                                   | tput voltage, VOH                                                         |          |     |          |      |     | 5.5  | V    |  |

| High-level ou                                   | tput current, IOH                                                         |          |     | - 10.3   |      |     |      | mA   |  |

| Low-level output current, IQL                   |                                                                           |          |     | 16       |      |     | 16   | mA   |  |

| Width of write pulse (write enable low), tw(wr) |                                                                           | 65       |     |          | 65   |     | _    | ns   |  |

| ин                                              | Address before write pulse, t <sub>Su(ad)</sub>                           | 01       |     |          | Οţ   |     |      |      |  |

| Setup time                                      | Data before end of write pulse, t <sub>su(da)</sub>                       | 65↑      |     |          | 65↑  |     |      | ns   |  |

|                                                 | Chip-select before end of write pulse, t <sub>Su</sub> (\$\overline{S}\$) | 65↑      |     |          | 65↑  |     |      | 1    |  |

|                                                 | Address after write pulse, th(ad)                                         | 01       |     |          | 01   |     |      |      |  |

| Hold time                                       | Data after write pulse, th(da)                                            | 01       |     |          | 01   |     |      | ns   |  |

|                                                 | Chip-select after write pulse, th(S)                                      | 01       |     |          | 01   |     |      | ]    |  |

| Operating fre                                   | e-air temperature, TA                                                     | 0        |     | 70       | 0    |     | 70   | °C   |  |

<sup>†</sup> The arrow indicates the transition of the write-enable input used for reference: I for the low-to-high transition, I for the high-to-low transition.

NOTE 1: Voltage values are with respect to network ground terminal.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                  |                                                         |                                                                                                                       |      | 'S201            |       | 'S301    |      |           |      |

|------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------------------|-------|----------|------|-----------|------|

| PARAMETER        |                                                         | TEST CONDITIONS <sup>†</sup>                                                                                          |      | TYP <sup>‡</sup> | MAX   | MIN      | TYP‡ | MAX       | UNIT |

| ViH              | High-level input voltage                                |                                                                                                                       | 2    |                  |       | 2        |      |           | V    |

| VIL              | Low-level input voltage                                 |                                                                                                                       |      |                  | 0.8   |          |      | 0.8       | V    |

| VIK              | Input clamp voltage                                     | $V_{CC} = MIN$ , $I_{\parallel} = -18 \text{ mA}$                                                                     |      |                  | - 1.2 |          |      | - 1.2     | ٧    |

| ∨он              | High-level output voltage                               | $V_{CC}$ = MIN, $V_{IH}$ = 2 V,<br>$V_{IL}$ = 0.8 V, $I_{OH}$ = MAX                                                   | 2.4  |                  |       |          |      |           | ٧    |

| VOL              | Low-level output voltage                                | VCC = MIN, VIH = 2 V, IOL = 16 mA                                                                                     |      |                  | 0.45  |          |      | 0.45      | V    |

| юн               | High-level output current                               | $V_{CC} = MIN$ , $V_{IH} = 2 \text{ V}$ , $V_{O} = 2.4 \text{ V}$<br>$V_{IL} = 0.8 \text{ V}$ $V_{O} = 5.5 \text{ V}$ |      |                  |       |          |      | 40<br>100 | μΑ   |

| lozh             | Off-state output current,<br>high-level voltage applied | $V_{CC} = MAX$ , $V_{IH} = 2 V$ , $V_{IL} = 0.8 V$ , $V_{OH} = 2.4 V$                                                 |      |                  | 40    |          |      |           | μА   |

| I <sub>OZL</sub> | Off-state output current, low-level voltage applied     | $V_{CC} = MAX, V_{IH} = 2 V,$<br>$V_{IL} = 0.8 V, V_{OL} = 0.5 V$                                                     |      |                  | - 40  |          |      |           | μΑ   |

| l <sub>I</sub>   | Input current at maximum input voltage                  | V <sub>CC</sub> = MAX, V <sub>1</sub> = 5.5 V                                                                         |      |                  | 1     |          |      | 1         | mA   |

| Iн .             | High-level input current                                | $V_{CC} = MAX$ , $V_1 = 2.7 V$                                                                                        |      |                  | 25    |          |      | 25        | μΑ   |

| IIL.             | Low-level input current                                 | V <sub>CC</sub> - MAX, V <sub>I</sub> = 0.5 V                                                                         |      |                  | - 250 |          |      | - 250     | μΑ   |

| los              | Short-circuit output current §                          | V <sub>CC</sub> - MAX                                                                                                 | - 30 |                  | - 100 |          |      |           | mA   |

| lcc              | Supply current                                          | V <sub>CC</sub> = MAX, See Note 2                                                                                     |      | 100              | 140   | <u> </u> | 100  | 140       | mA   |

<sup>&</sup>lt;sup>†</sup>For conditions shown as MIN or MAX use the appropriate value specified under recommended operating conditions.

$<sup>^{\</sup>ddagger}$ All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

<sup>§</sup>Duration of the short circuit should not exceed one second.

NOTE 2: I<sub>CC</sub> is measured with all chip-select inputs grounded, all other inputs at 4.5 V, and the output open.

# '\$201 switching characteristics over recommended operating ranges of TA and VCC (unless otherwise noted)

|        | PARAMETER                                        |          | TEST CONDITIONS         | MiN | TYP <sup>‡</sup> | MAX   | UNIT |

|--------|--------------------------------------------------|----------|-------------------------|-----|------------------|-------|------|

| ta(ad) | ta(S) Access time from chip select (select time) |          | C <sub>1</sub> = 30 pF, |     | 42               | 65    | ns   |

| ta(S)  |                                                  |          | See Note 3              |     | 13               | 30    | ns   |

| tSR    |                                                  |          |                         |     | 20               | 40    | ns   |

| tPXZ   | Disable time from high or low level              | From S   | $C_{L} = 5 pF$ ,        |     |                  | 20    | ns   |

|        | Disable time from high or low level              | From R/W | See Note 3              | "   | 20               | 1 ''3 |      |

# 'S301 switching characteristics over recommended operating ranges of TA and VCC (unless otherwise noted)

|        | PARAMETER                                       |        | TEST CONDITIONS                                  | MIN TYP‡ | MAX | UNIT  |

|--------|-------------------------------------------------|--------|--------------------------------------------------|----------|-----|-------|

| ta(ad) | a(S) Access time from chip enable (enable time) |        | C <sub>I</sub> = 30 pF,                          | 42       | 65  | ns    |

| ta(S)  |                                                 |        | $R_{L1} = 300 \Omega,$<br>$R_{L2} = 600 \Omega,$ | 13       | 30  | ns    |

| tSR    |                                                 |        |                                                  | 20       | 40  | ns    |

|        | Propagation delay time, low-to-high-level       | From S | See Note 3                                       | 8        | 20  | ns    |

| tPLH   | output (disable time) From R/W                  |        | See Mote 3                                       | 15       | 35  | 1 ''s |

$^{\ddagger}AII$  typical values are at VCC = 5 V, TA = 25 °. NOTE 2: Load circuits and voltage waveforms are shown in Section 1.