# RNA51957A,B

## Voltage Detecting, System Resetting IC Series

REJ03D0912-0100 Rev.1.00 Oct 10, 2008

#### **Description**

RNA51957A,B are semiconductor integrated circuits for resetting of all types of logic circuits such as CPUs, and has the feature of setting the detection voltage by adding external resistance.

They include a built-in delay circuit to provide the desired retardation time simply by adding an external capacitor. They fined extensive applications, including battery checking circuit, level detecting circuit and waveform shaping circuit.

#### **Features**

- · Few external parts

- Large delay time with a capacitor of small capacitance (td  $\approx 100$  ms, at 0.33 µF)

- Low threshold operating voltage (Supply voltage to keep low-state at low supply voltage): 0.6 V (Typ) at  $R_L = 22 \text{ k}\Omega$

- Wide supply voltage range: 2 V to 17 V

- Wide application range

- Ordering Information

| Part Name     | Package Type | Package Code | Package<br>Abbreviation | Taping Abbreviation (Quantity) | Surface<br>Treatment |

|---------------|--------------|--------------|-------------------------|--------------------------------|----------------------|

| RNA51957AFPH0 | SOP-8 pin    | PRSP0008DE-C | FP                      | H (2,500 pcs / Reel)           | 0 (Ni/Pd/Au)         |

| RNA51957BFPH0 | SOP-8 pin    | PRSP0008DE-C | FP                      | H (2,500 pcs / Reel)           | 0 (Ni/Pd/Au)         |

### **Application**

Reset circuit of Pch, Nch, CMOS, microcomputer, CPU and MCU, Reset of logic circuit, Battery check circuit, switching circuit back-up voltage, level detecting circuit, waveform shaping circuit, delay waveform generating circuit, DC/DC converter, over voltage protection circuit

### **Recommended Operating Condition**

• Supply voltage range: 2 V to 17 V

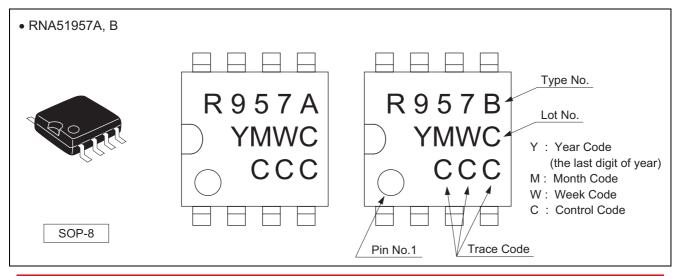

#### **Outline and Article Indication**

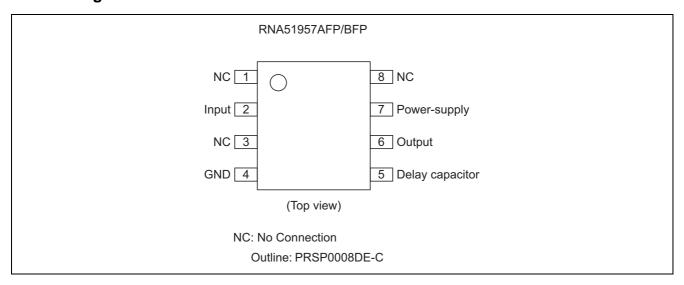

### **Pin Arrangement**

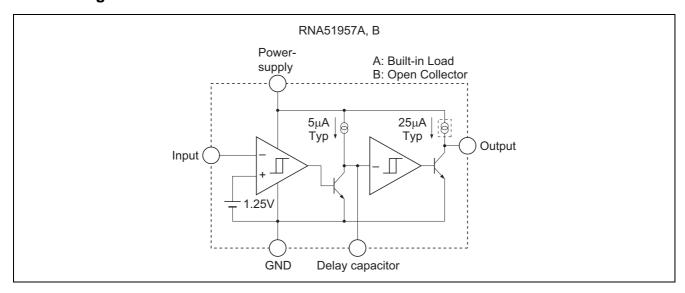

## **Block Diagram**

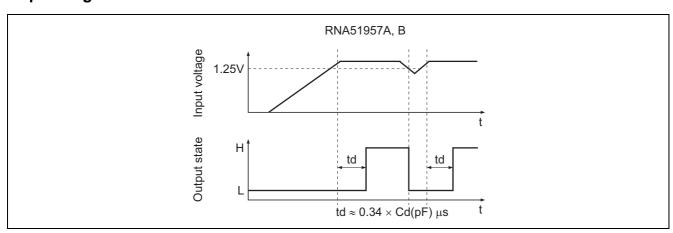

## **Operating Waveform**

## **Absolute Maximum Ratings**

( $Ta = 25^{\circ}C$ , unless otherwise noted)

| Item                  | Symbol          | Ratings                               | Unit  |                                                 | Conditions               |

|-----------------------|-----------------|---------------------------------------|-------|-------------------------------------------------|--------------------------|

| Supply voltage        | Vcc             | 18                                    | V     |                                                 |                          |

| Output sink current   | Isink           | 6                                     | mA    |                                                 |                          |

| Output valtage        | Vo              | V <sub>CC</sub>                       | V     | Type A (output with constant current load)      |                          |

| Output voltage        |                 | 18                                    | V     | Type B (open collector output)                  |                          |

| Power dissipation     | Pd              | 400                                   | mW    | 8-pin SOP (PRSP0008DE-C)                        |                          |

| Thermal derating      | Kθ              | 4.4                                   | mW/°C | Refer to the thermal derating curve.            | 8-pin SOP (PRSP0008DE-C) |

| Operating temperature | Topr            | -40 to +85                            | °C    |                                                 |                          |

| Storage temperature   | Tstg            | -55 to +125                           | °C    |                                                 |                          |

| Input voltage range   | V <sub>IN</sub> | -0.3 to V <sub>CC</sub><br>-0.3 to +7 | V     | $V_{CC} \le 7 \text{ V}$ $V_{CC} > 7 \text{ V}$ |                          |

### **Electrical Characteristics**

(Ta = 25°C, unless otherwise noted)

### • "L" reset type

| Item                                      | Symbol             | Min                  | Тур                   | Max      | Unit | Test Conditions                                                         |                                      |

|-------------------------------------------|--------------------|----------------------|-----------------------|----------|------|-------------------------------------------------------------------------|--------------------------------------|

| Detecting voltage                         | Vs                 | 1.20                 | 1.25                  | 1.30     | V    |                                                                         |                                      |

| Hysteresis voltage                        | $\Delta V_S$       | 9                    | 15                    | 23       | mV   | V <sub>CC</sub> = 5V                                                    |                                      |

| Detecting voltage temperature coefficient | V <sub>S</sub> /ΔT | _                    | 0.01                  |          | %/°C |                                                                         |                                      |

| Supply voltage range                      | $V_{CC}$           | 2                    | _                     | 17       | V    |                                                                         |                                      |

| land delicate and an                      | \ /:               | -0.3                 | _                     | $V_{CC}$ | V    | $V_{CC} \le 7V$                                                         |                                      |

| Input voltage range                       | Vin                | -0.3                 | _                     | 7.0      | ľ    | V <sub>CC</sub> > 7V                                                    |                                      |

| Input current                             | I <sub>IN</sub>    | _                    | 100                   | 500      | nA   | V <sub>IN</sub> = 1.25V                                                 |                                      |

| 0''1                                      | Icc                | _                    | 390                   | 590      |      | Type A, V <sub>CC</sub> = 5V                                            |                                      |

| Circuit current                           |                    | _                    | 360                   | 540      | μА   | Type B, V <sub>CC</sub> = 5V                                            |                                      |

| Delay time                                | t <sub>pd</sub>    | 1.6                  | 3.4                   | 7.0      | ms   | Cd = 0.01µF *                                                           |                                      |

| Output saturation voltage                 | Vsat               | _                    | 0.2                   | 0.4      | V    | L reset type, V <sub>CC</sub> = 5V, V <sub>IN</sub> < 1.2V, Isink = 4mA |                                      |

| Threshold operating                       | V <sub>OPL</sub>   | _                    | 0.67                  | 8.0      | V    | L reset type minimum supply voltage for IC operation                    | $R_L = 2.2k\Omega$ , $Vsat \le 0.4V$ |

| voltage                                   |                    | _                    | 0.55                  | 0.7      |      |                                                                         | $R_L = 100k\Omega$ , $Vsat \le 0.4V$ |

| Output leakage current                    | I <sub>OH</sub>    | _                    | _                     | 30       | nA   | Туре В                                                                  |                                      |

| Output load current                       | I <sub>oc</sub>    | -40                  | -25                   | -17      | μΑ   | Type A, $V_{CC} = 5V$ , $V_O = 1/2 \times V_{CC}$                       |                                      |

| Output high voltage                       | V <sub>OH</sub>    | V <sub>CC</sub> -0.2 | V <sub>CC</sub> -0.06 | _        | V    | Type A                                                                  |                                      |

Note: Please set the desired delay time by attaching capacitor of the range between 4700 pF and 10  $\mu$ F.

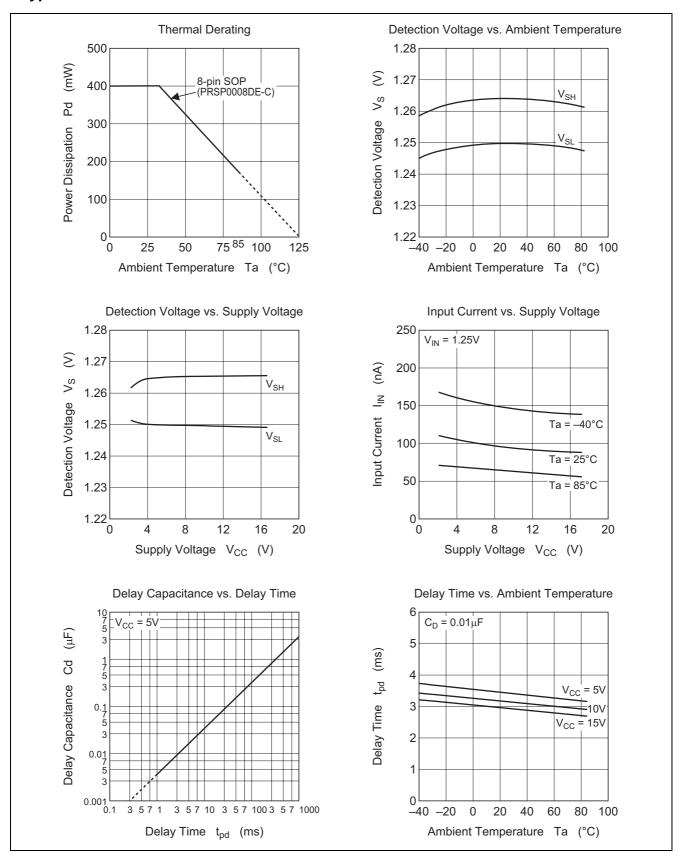

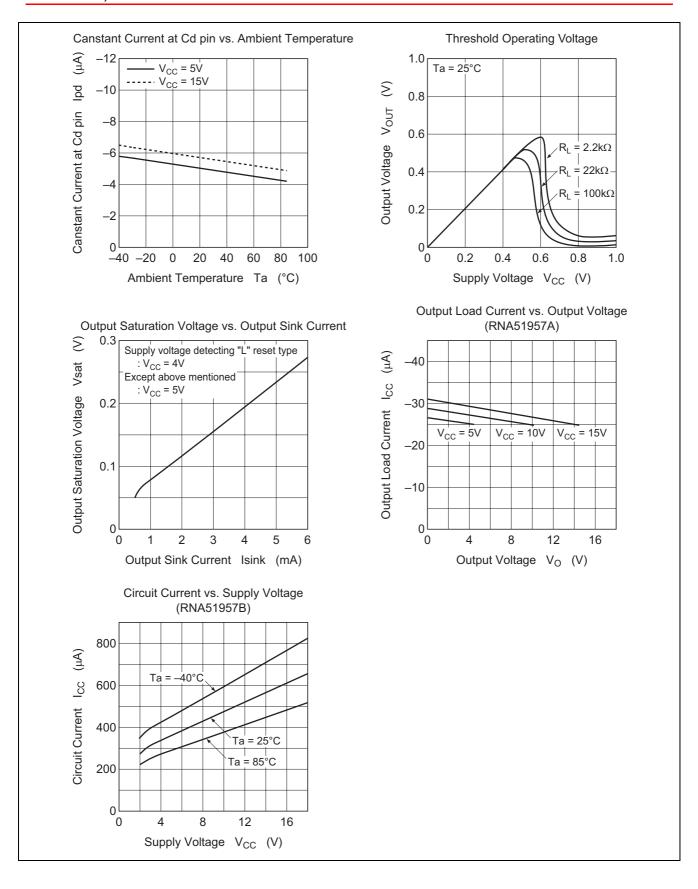

### **Typical Characteristics**

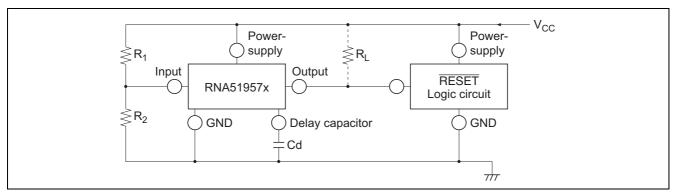

#### **Example of Application Circuit**

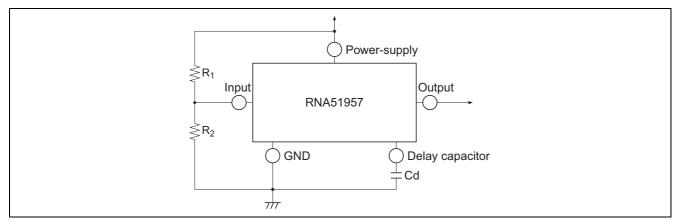

#### **Reset Circuit of RNA51957**

Figure 1 Reset Circuit of RNA51957

Notes: 1. When the detecting supply voltage is 4.25 V, RNA51953 are used. In this case,  $R_1$  and  $R_2$  are not necessary. When the voltage is anything except 4.25 V, RNA51957 are used. In this case, the detecting supply voltage is  $1.25 \times (R_1 + R_2)/R_2$  (V) approximately. The detecting supply voltage can be set between 2 V and 15 V.

- 2. If a longer delay time is necessary, RNA51953, RNA51957 are used. In this case, the delay time is about  $0.34 \times Cd$  (pF)  $\mu s$ .

- 3. If the RNA51957 and the logic circuit share a common power source, type A (built-in load type) can be used whether a pull-up resistor is included in the logic circuit or not.

- 4. The logic circuit preferably should not have a pull-down resistor, but if one is present, add load resistor  $R_L$  to overcome the pull-down resistor.

- 5. When the reset terminal in the logic circuit is of the low reset type, RNA51953 and RNA51957 are used.

- 6. When a negative supply voltage is used, the supply voltage side of RNA51957 and the GND side are connected to negative supply voltage respectively.

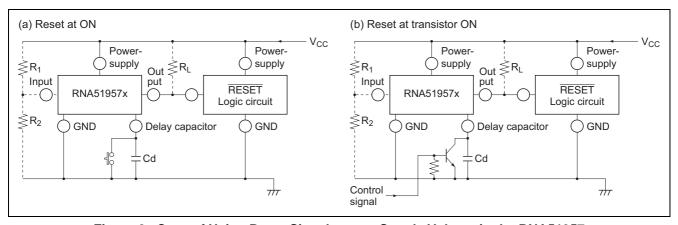

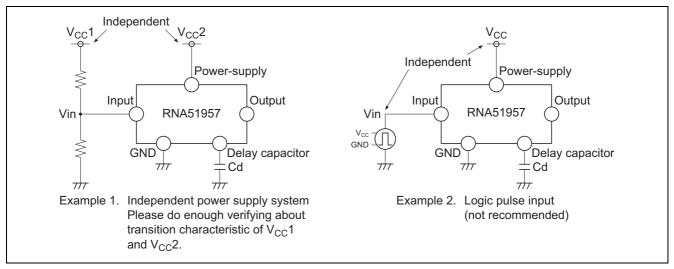

#### Case of Using Reset Signal except Supply Voltage in the RNA51957

Figure 2 Case of Using Reset Signal except Supply Voltage in the RNA51957

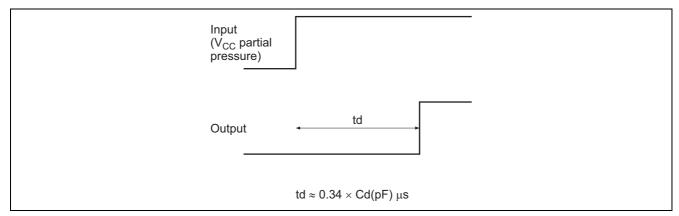

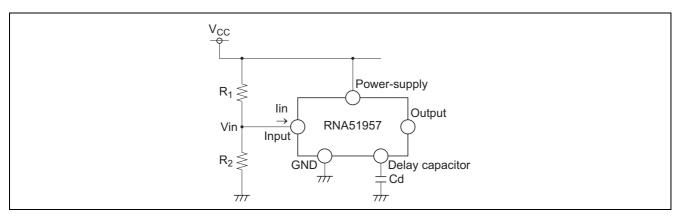

### **Delay Waveform Generating Circuit**

When RNA51957 are used, a waveform with a large delay time can generate only by adding a small capacitor.

Figure 3 Delay Waveform Generating Circuit

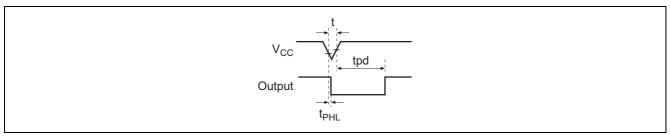

### **Operating Waveform**

Figure 4 Operating Waveform

#### Notice for use

#### **About the Power Supply Line**

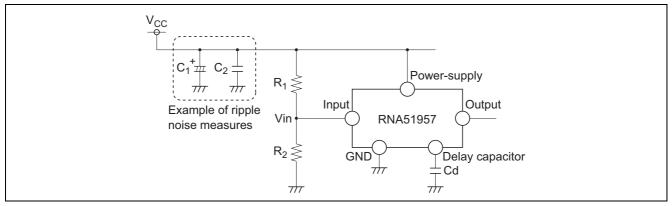

1. About bypass capacitor

Because the ripple and the spike of the high frequency noise and the low frequency are superimposed to the power supply line, it is necessary to remove these.

Therefore, please install  $C_1$  and  $C_2$  for the low frequency and for the high frequency between the power supply line and the GND line as shown in following figure 5.

Figure 5 Example of Ripple Noise Measures

2. The sequence of voltage impression

Please do not impress the voltages to the input terminals earlier than the power supply terminal. Moreover, please do not open the power supply terminal with the voltage impressed to the input terminal.

(The setting of the bias of an internal circuit collapses, and a parasitic element might operate.)

#### **About the Input Terminal**

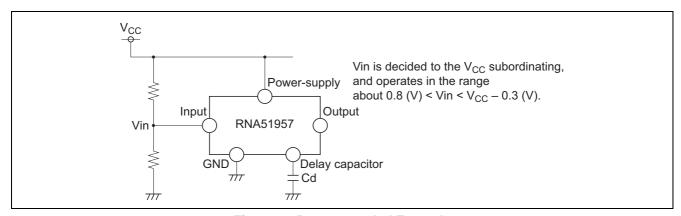

1. Setting range of input voltage

The following voltage is recommended to be input to the input terminal (pin 2).

about 0.8 (V) < Vin <

$$V_{CC} - 0.3$$

(V) ... at  $V_{CC} \le 7$  V about 0.8 (V) < Vin < 6.7 (V) ...... at  $V_{CC} > 7$  V

2. About using input terminal

Please do an enough verification to the transition characteristic etc. of the power supply when using independent power supply to input terminal (pin 2).

Figure 6 Recommended Example

Figure 7

### 3. Calculation of detecting voltage

Detecting voltage Vs can be calculated by the following expression.

However, the error margin is caused in the detecting voltage because input current Iin (standard 100 nA) exists if it sets too big resistance.

Please set the constant to disregard this error margin.

$$V_S = 1.25 \times \left(\frac{R_1 + R_2}{R_2}\right) + \frac{\text{lin} \times R_1}{\text{error margin}}$$

Figure 8 Influence of Input Current

#### 4. About the voltage input outside ratings

Please do not input the voltage outside ratings to the input terminal.

An internal protection diode becomes order bias, and a large current flows.

#### **Setting of Delay Capacity**

Please use capacitor Cd for the delay within the range of 10 µF or less.

When a value that is bigger than this is set, the problem such as following (1), (2), and (3) becomes remarkable.

Figure 9 Time Chart at Momentary Voltage-Decrease

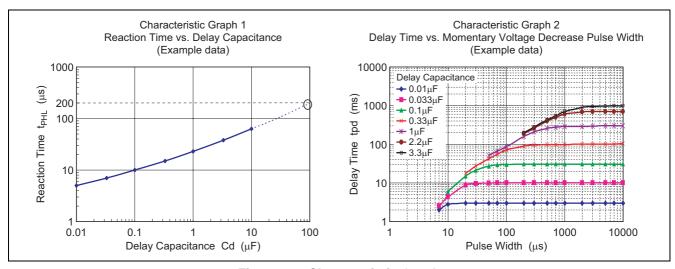

(1) The difference at delay time becomes remarkable.

A long delay setting of tens of seconds is fundamentally possible. However, when set delay time is lengthened, the range of the difference relatively grows, too. When a set value is assumed to be 'tpd', the difference occurs in the range from  $0.47 \times$  tpd to  $2.05 \times$  tpd. For instance, 34 seconds can be calculated at  $100 \, \mu F$ . However, it is likely to vary within the ranges of 16-70 seconds.

(2) Difficulty to react to a momentary voltage decrease.

For example, the reaction time  $t_{PHL}$  is 10 µs when delay capacitor Cd = 0.1 µF.

The momentary voltage-decrease that is longer than such  $t_{PHL}$  are occurs, the detection becomes possible. When the delay capacitance is enlarged,  $t_{PHL}$  also becomes long. For instance, it becomes about 100 to 200  $\mu$ s in case of circuit constant  $C1 = 100 \ \mu$ F.

(Characteristic graph 1 is used and extrapolation in case of Cd =  $100 \mu F$ .)

Therefore, it doesn't react to momentary voltage-decrease that is shorter than this.

(3) Original delay time is not obtained.

When the momentary voltage-decrease time 't' is equivalent to  $t_{PHL}$ , the discharge becomes insufficient and the charge starts at that state. This phenomenon occurs at large capacitance. And, original delay time tpd is not obtained.

Please refer to characteristic graph 2. (Delay time versus input pulse width)

Figure 10 Characteristic Graph

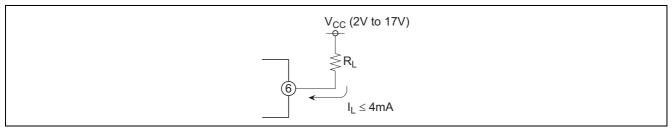

#### Setting of Output Load Resistance (RNA51957B)

High level output voltage can be set without depending on the power-supply voltage because the output terminal is an open collector type. However, please guard the following notes.

- 1. Please set it in value (2 V to 17 V) within the range of the power-supply voltage recommendation.

Moreover, please never impress the voltage of maximum ratings 18 V or more even momentarily either.

- 2. Please set output load resistance (pull-up resistance)  $R_L$  so that the output current (output inflow current  $I_L$ ) at L level may become 4 mA or less. Moreover, please never exceed absolute maximum rating (6 mA).

Figure 11 Output Load Resistance R<sub>L</sub>

#### **Others**

- Notes when IC is handled are published in our reliability handbook, and please refer it.

The reliability handbook can be downloaded from our homepage (following URL).

http://www.renesas.com/fmwk.jsp?cnt=reliability\_root.jsp&fp=/products/common\_info/reliability

- 2. Additionally, please inquire of our company when there is an uncertain point on use.

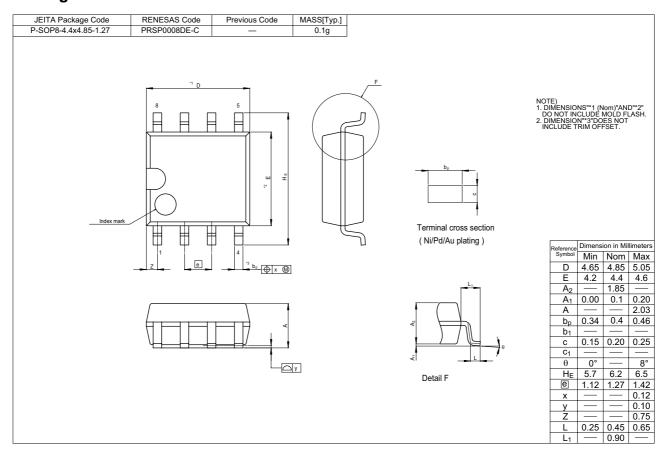

### **Package Dimensions**

Renesas Technology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas lechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warrantes or representations with respect to the accuracy or completeness of the information in this document nor grants any license to any intellectual property girbs to any other rights of representations with respect to the information in this document in this document of the purpose of the respect of the information in this document in the product data, diagrams, charts, programs, algorithms, and application circuit examples.

3. You should not use the products of the technology described in this document for the purpose of military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations, and procedures required to change without any plan protein. Before purchasing or using any Renesas products listed in this document, in the development is satisfied. The procedure is such as the development of the dev

#### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510